# One-size-fits-all PLLs for Advanced Samsung Foundry Processes

Andrew Cole, VP

## **Silicon Creations Overview**

- IP provider of PLLs, Oscillators and High-speed Interfaces

- Founded 2006 self-funded, profitable and growing

- Design offices in Atlanta, USA and Krakow, Poland

- High quality development, award winning support

- >330 customers (>130 in China)

- Mass production in many FinFET process nodes with PLL IPs ready now down to Samsung Foundry 4nm LPE

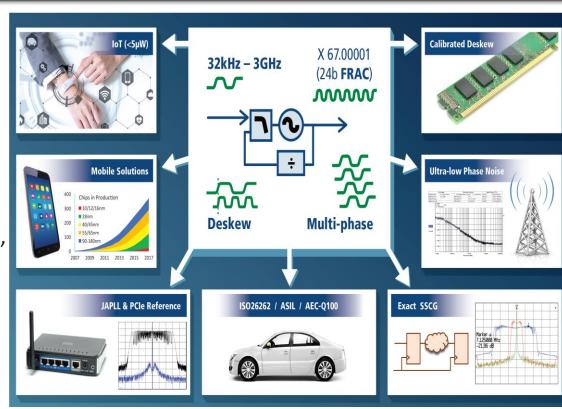

## **PLLs from Silicon Creations**

Highest volume analog IPs

. . .

Our PLLs have been produced on millions of wafers

. . .

robust design and good QA are essential

- PLL products include general purpose, fractional, low jitter AFE, μW IoT, Automotive

- PLLs available now in Samsung Foundry 28FDSOI and FinFET processes from 10LPP/LPE to 4LPE

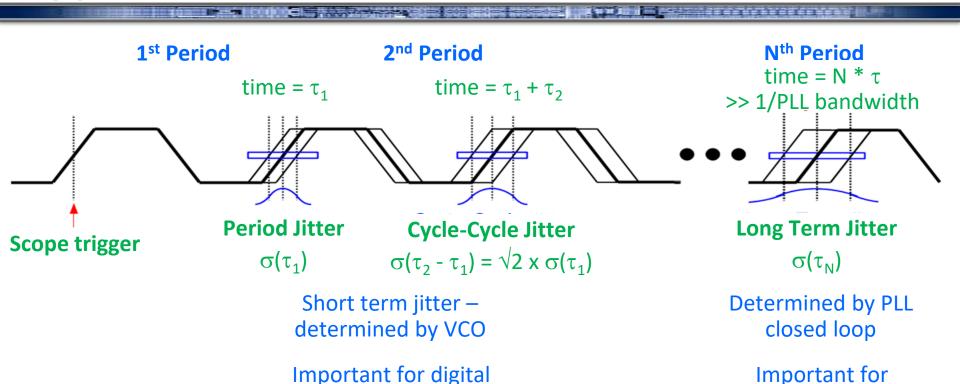

# **Types of Jitter**

ADC/DAC and SerDes

timing ("STA")

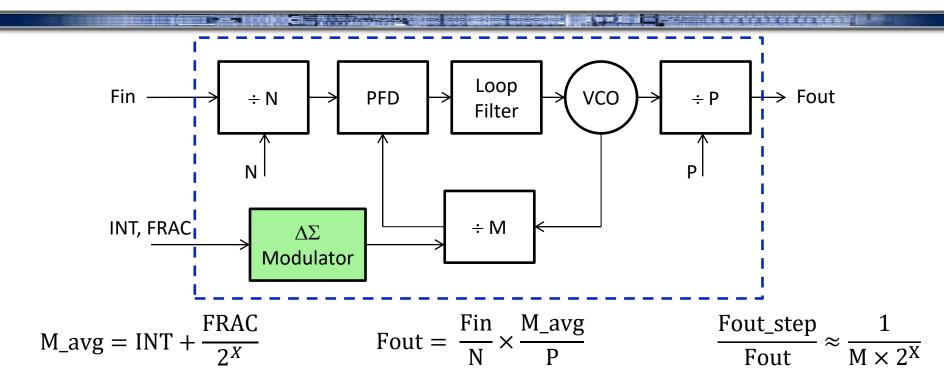

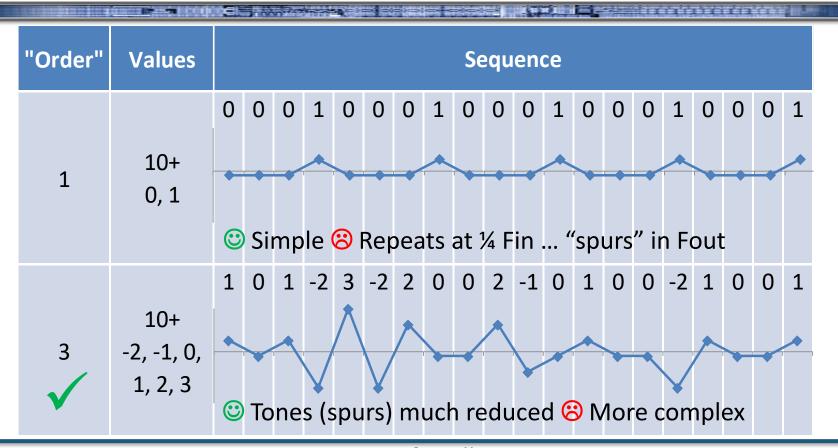

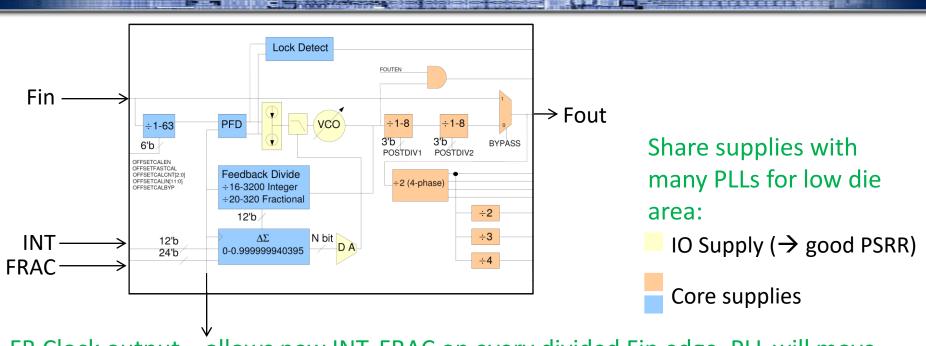

#### Fractional-N PLL

With x = 24 (bits), typical M > 20, LSB change in Fout < 0.003ppm (>10,000ppm for integer PLL)

## E.g. Average FBDIV of 10.25

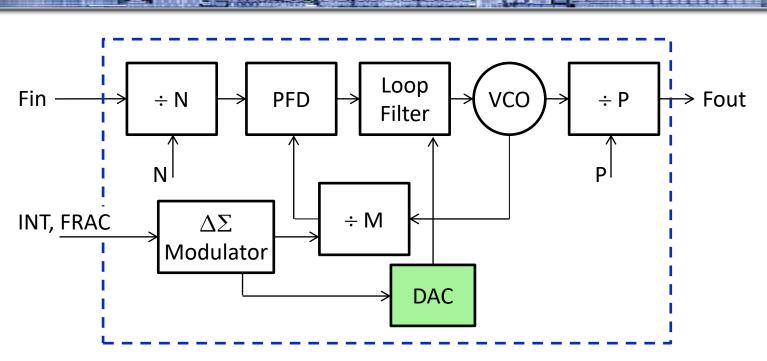

## **DAC to Fix Fractional Jitter**

Feed inverse of impulse errors forward to loop filter. DAC re-uses existing transistors and current, so adds almost no area, and almost no power.

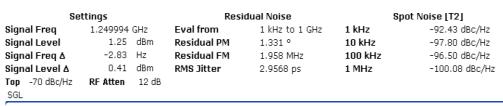

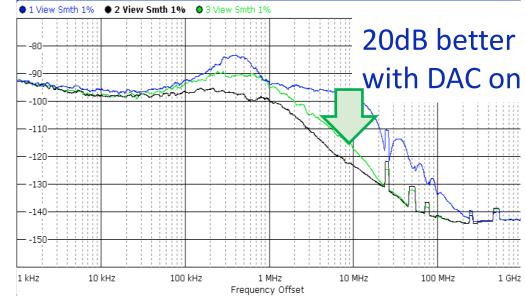

## **DAC Performance Measured**

Phase noise with and without DAC. Performance is improved dramatically.

- ✓ Flexible: Any output frequency with any Xtal

- ✓ Good PPA: Use FRAC PLL to make a low jitter clock e.g. SRIS clock for PCIe

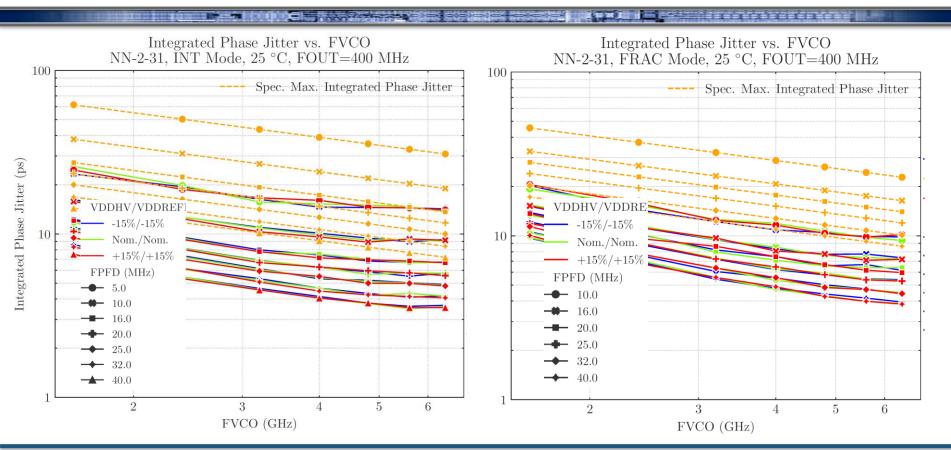

## Measurement – SS5LPe

# **DFS & Supply Sharing**

FB Clock output – allows new INT, FRAC on every divided Fin edge. PLL will move predictably to new programmed frequency without losing LOCK for Dynamic Frequency Scaling (DFS).

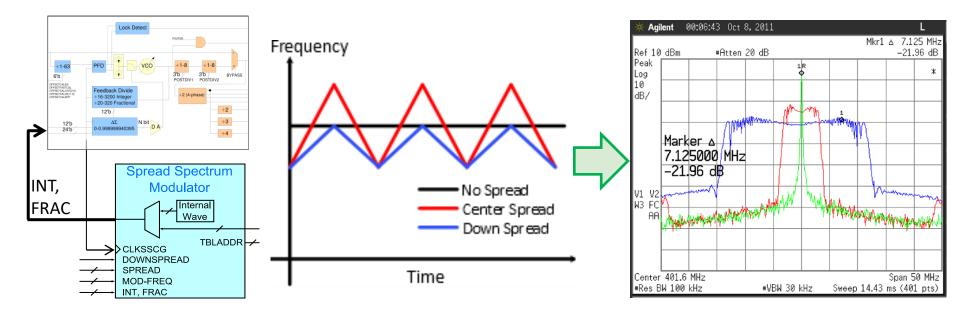

# **Exact Spread Spectrum**

Digital modulator continuously changes the target frequency for exact spread spectrum shape & modulation frequency. Soft IP (RTL), 4k gates

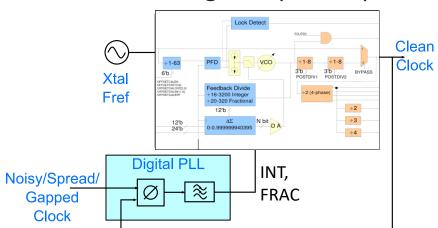

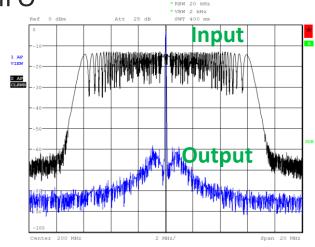

## **Jitter Cleaner PLL**

- Digital Filter (RTL ≈19k gates) sets multiplier for fixed clock for FRAC PLL

- Integrated LTJ <1ps and Bandwidth <1Hz possible ... replaces \$8 to \$30 external chip</li>

- Cleans jitter in noisy recovered clock for Sync-E or Optical Networking; Generates average of spread spectrum input for FIFO

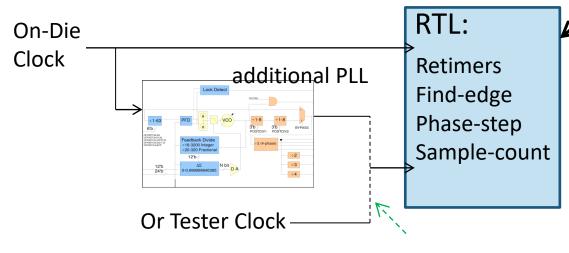

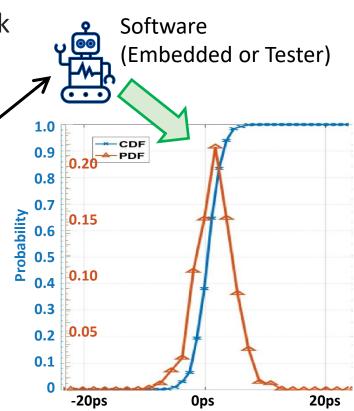

## **Jitter Monitor**

Measures jitter and duty cycle of on-chip clock

Synthesizable RTL

Spare FRAC PLL enables chip to test itself Or Production Test mode

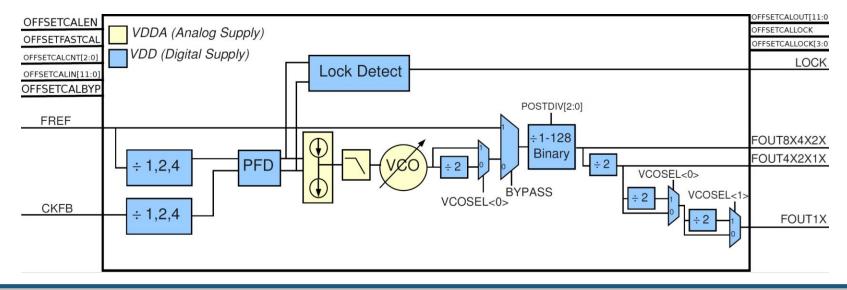

## **Deskew PLLs**

- Core voltage only: easy to integrate and low power

- Below 0.01mm<sup>2</sup>

- Self-calibration of device mismatch

## **Summary**

- Silicon Creations has been providing reliable, high-performance clocking and SerDes solutions since 2006

- Our Fractional-N PLL is production proven with the highest volumes of any mixed signal IP; Collaboration with Samsung Foundry has helped us provide silicon proven FRAC PLLs in 28FDSOI, 10LPP/LPE, 7LPP, and 5LPP with 4LPE silicon expected soon

- Fractional-N PLLs together with RTL provide very flexible solutions to complex problems with low risk while reducing system BOM or reducing test cost

- For more information, please contact <a href="mailto:sales@siliconcr.com">sales@siliconcr.com</a> or visit our booth #1338 on the ground floor