#### Content slide

- About Silicon Creations

- SoC architecture & clocking options

- Clocking IP Portfolio

- Key performance metrics and related applications

- Optimized clocking solutions

- Factors affecting jitter

- Support during implementation & Tape-out

- Summary and Conclusions

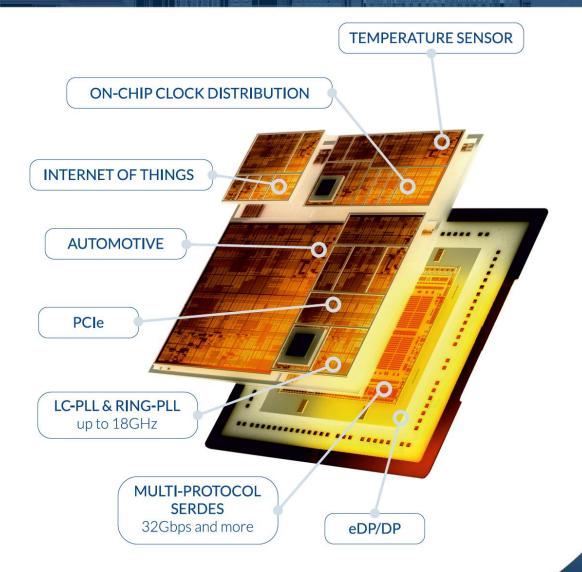

# PLLs, Oscillators & High-speed Interfaces

#### Silicon Creations in numbers

1500+

Chips using our IP

700+

**Unique IP products**

150+

Production tape-outs annually

11M+

12" wafers shipped using our IP

500+

**Customers**

2nm

**Available today**

**Automotive**

# Silicon Creations IP in today SOCs

General-Purpose & Specialized **PLLs** +**RTL** upgrades

High-Performance LVDS I/O

Multiprotocol SerDes

**Oscillators & XO**

**CML cells** for On-Chip Signaling

SerDes

**Oscillators**

# **Optimized Clocking IP Portfolio**

#### **General Purpose IP**

INT PLL

FRAC PLL

XO 8-40MHz OSC 1-24MHz

DESKEW

BAND-GAP

PoR

TSENSE

Delay-to -Digital DDC

# Low-Power /Low-Area PLL

Low-BW LBINT IoT

Low-Area LAFRAC

Low-Area LAINT Low-Power LPFRAC

# High-Performance /Specialized PLL

Frequency Generator FG

8/16-PHASE MPINT

High-BW HBFRAC

Low-Jitter LJFRAC

LC-PLL

Low-Jitter LJINT

#### **Clock Distribution**

DIVIDER

CMLMUX

LVDS Tx/Rx

#### **Supplementary RTL**

JITTER -CLEANER DPLL

Spread -Spectrum SSMOD

Digital Phase Aligner DPA

Jitter -Monitor JMON

Frequency Jumper LOCK COUNTER

#### **Automotive**

**FMEDA**

SAFETY MANUAL

DFMEA

#### Legend

**PLL**

Analog IP

Clock

distribution

Documentation

RTL IP

Oscillators

-6

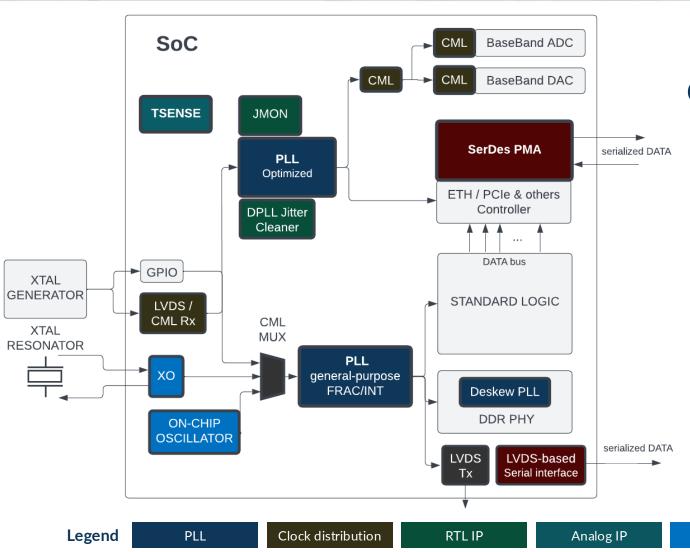

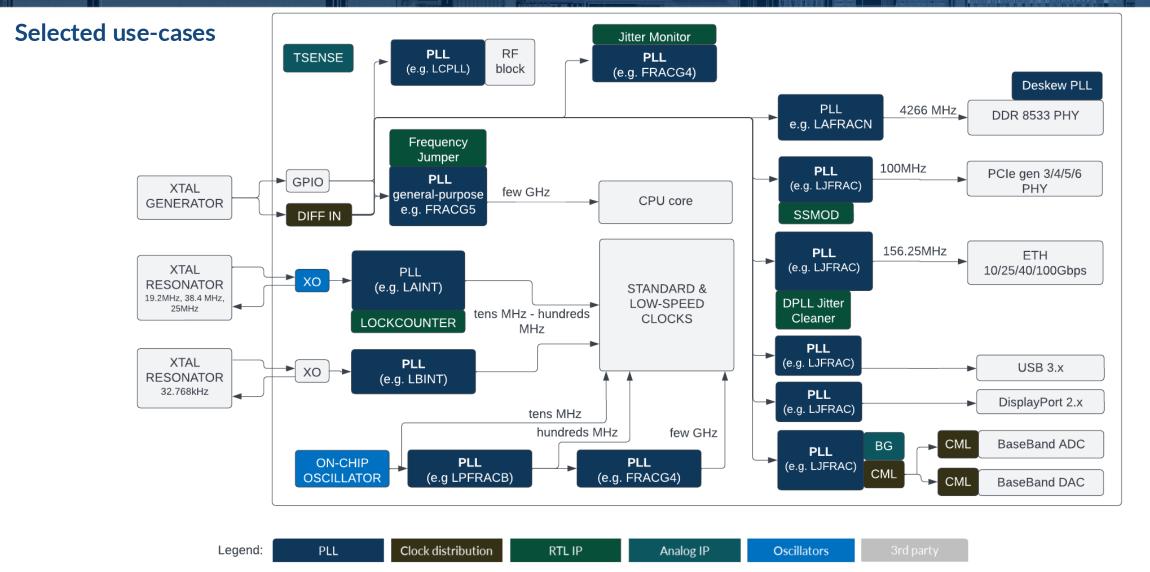

# SoC Clocking Options using specialized SiCr IP

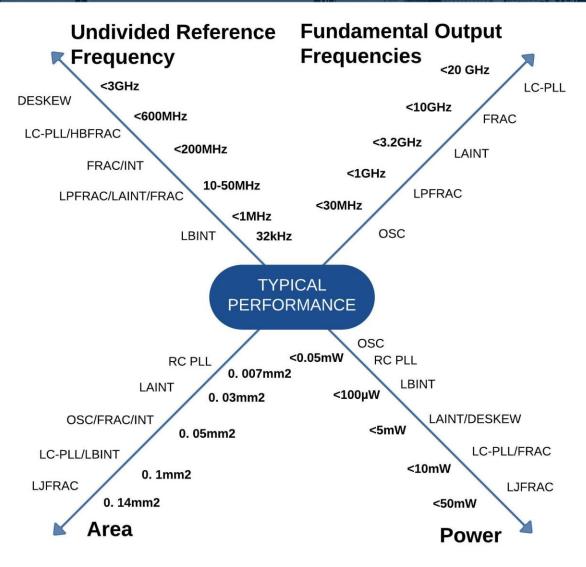

# PLL Performance Matrix: Frequency, Area, Power

Silicon Creations PLL IP covers a vast range of performance indicators and can be a fit to many applications.

- Power: below 50 μW through 5mW up to 50mW

- **Area:** 0.07mm<sup>2</sup> through 0.1mm<sup>2</sup> up to 0.14mm<sup>2</sup>

- Output Frequency Range: From MHz range up to tens of GHz; frequency jumping, glitch-free operation, deskewing

- Reference Frequency Range: From 32kHz, through all crystal oscillator types, external clock chips, on-chip deskewing.

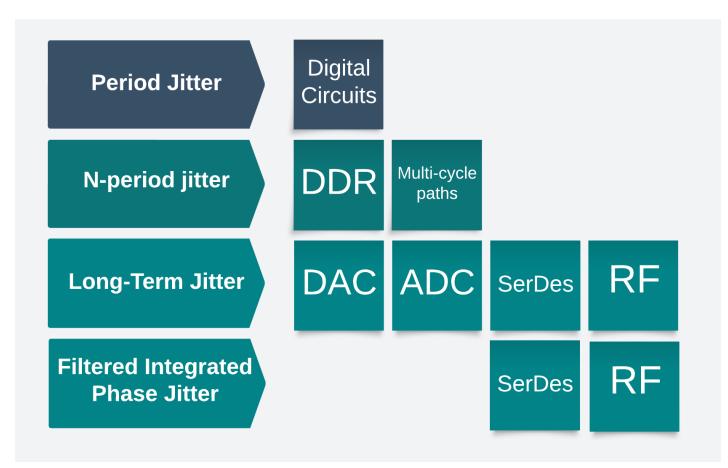

# Jitter types by application

# Various applications require different clock quality metrics.

- **Generic, digital synchronous logic:** Total period jitter (peak-negative) to define clock uncertainty for STA.

- Multi-cycle paths and e.g. DDR controllers: N-period jitter (depending on number of cycles / latency)

- ADC/DAC: Long-term jitter / Phase Noise to achieve ENOB; LJT reduces ENOB

- RF: Long-term jitter / Phase Noise to low EVM;

LTJ rotates constellation increasing EVM

- SerDes: Clock Specification (including integration bands) tightly related to the protocol and PHY vendor. Possible filtering (e.g. PCle spec). Embedded clock applications require low LJT.

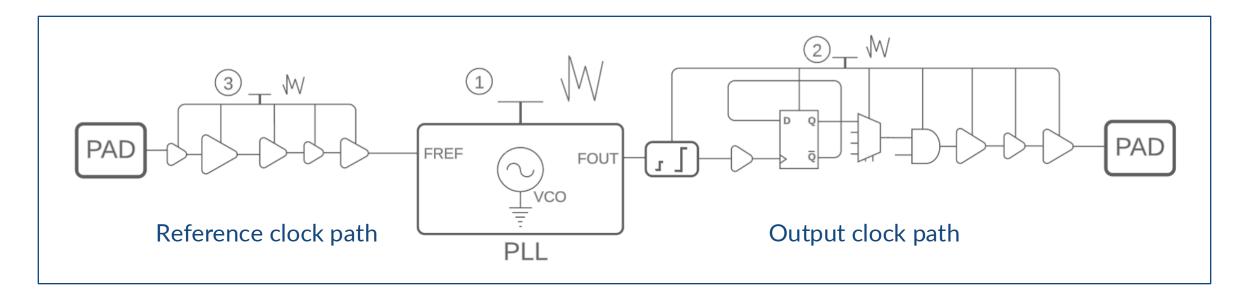

#### **Sources of Jitter**

#### Several factors impact jitter in SoC environments, but their effects vary significantly. Key contributors include:

- FREF signal quality including impact from its signal path -> design choices

- PLL design and operating point (FPFD, FVCO, FOUT configuration, PVT condition) -> IP vendor + Programming

- PLL conditions (decoupling, supply noise) -> IP vendor support + design choices

- Output clock path (supply noise, length / delay, additive jitter) -> design choices

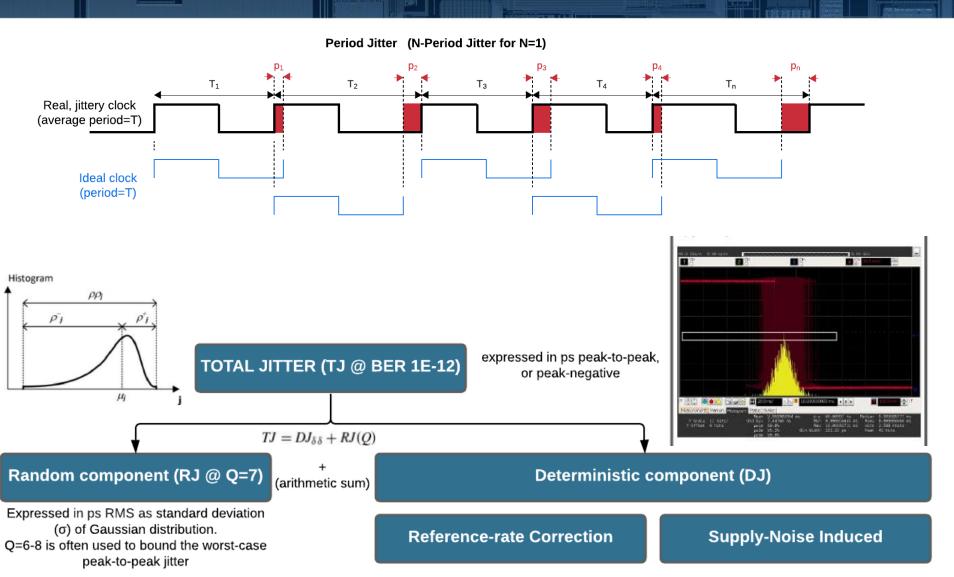

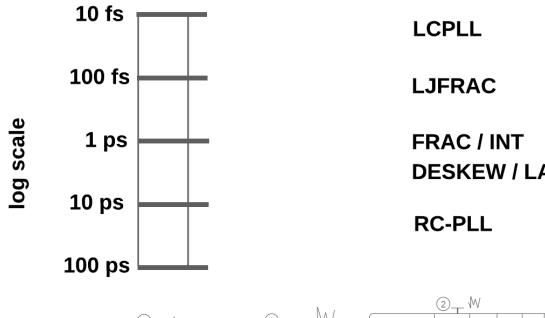

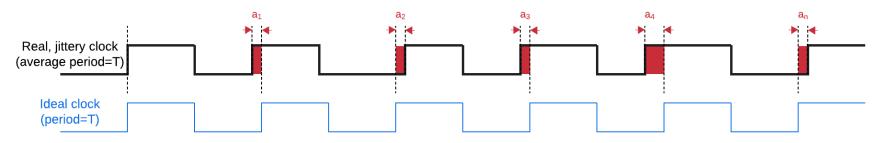

### Types of jitter: Period Jitter

#### **Period Jitter**

- Period Jitter is the deviation of each period from the ideal.

- Primary concern for digital clocking

- PJ can be natively measured by oscilloscope

- Peak-to-Peak jitter, or period jitter @ BER, can be estimated by jitter decomposition and using crest factor

# **Period Jitter & System Contributions**

#### **Period Jitter RMS (random)**

at equivalent 400MHz carrier (subject to scaling: the higher FOUT the lower period jitter)

Reference clock path

Ţvco

#### **IP Group** (exemplary)

**DESKEW / LAINT**

Output clock path

#### Important design aspects for best performance

- Low supply noise of clock tree (+PDN impedance)

- Short output clock path

- Period-jitter optimized output IO

- Low noise VDDIO=VDDHV analog supply

- **→** FREF(FPFD) **→** jitter

- **7**FVCO **3**iitter

- Jitter-optimized XO, GPIO or differential Rx

- Frequency stability of FREF source (e.g. crystal)

Importance depends on the target jitter specs. Consult your IP vendor.

# Types of Jitter: Long-Term Jitter (TIE)

#### Long-Term Jitter example: Absolute Jitter

# Trigger Voltage Controlled Oscillator Trig Input $\log(\sigma_{\Delta t})$ $\log(\sigma_{\Delta t})$ $\log(\sigma_{\Delta t})$ $\log(\sigma_{\Delta t})$ $\log(\sigma_{\Delta t})$ $\sigma_{1}*N^{1/2}$ $\sigma_{1}*N^{1/2}$ $\sigma_{1}*N^{1/2}$

**N-Period Jitter**

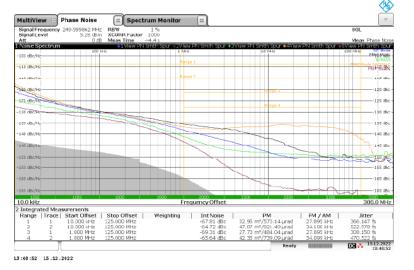

#### Phase Noise

#### Silicon Creations.

#### **Long Term Jitter**

- Long Term Jitter is the deviation of the output phase from the ideal. Output phase is the sum of all period errors.

- Primary concern for ADC/DAC, RF, SERDES.

- LTJ can be natively measured by oscilloscope or by integrating phase noise over certain frequency bands.

- Jitter can be decomposed into random and spurious components.

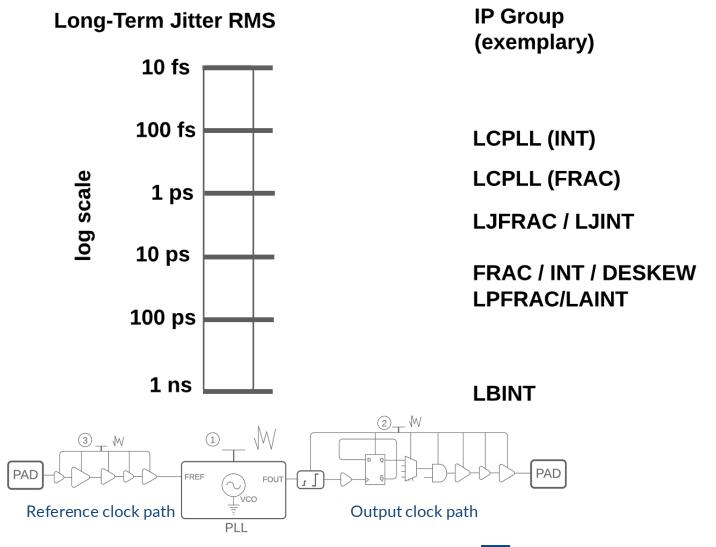

# Long-Term Jitter (TIE) & System Contributions

# Important design aspects for best performance

- FREF(FPFD) > jitter allows for higher PLL BW

- **≯**FVCO **¥**jitter

- Low noise VDDIO=VDDHV analog supply

- Low phase-noise FREF source (e.g., High-quality XO, Clocking Chip)

- Phase Jitter-optimized XO, GPIO or differential Rx

- Phase-Jitter optimized GPIO or differential Tx as test point

### **IP Engagement Process**

Best in class support by engineering team throughout the whole process

• Silicon Creations engineering team is involved from the beginning to help design SoC clock systems, from IP through distribution to the power delivery network.

- Stringent performance requirements for the clocking systems (ultra-low jitter, low power, wide tuning range, and small form factor) mandate careful IP selection, design considerations, and optimization tradeoffs.

- Silicon Creations clocking/IO/XO IP portfolio is diversified and well-positioned to meet the demands of today's SoCs from 2nm up to 180nm.

- Best-quality IP with experienced support engineers are the key to first silicon success.

Please reach out to us with any questions or comments: support@siliconcr.com

2025 IP-SOC Days 16